cadence版图drc常见错误

软件: cadence

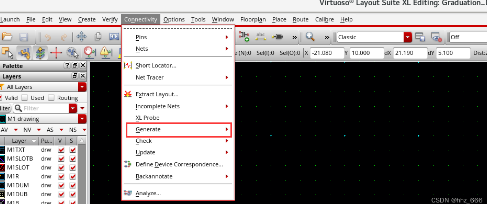

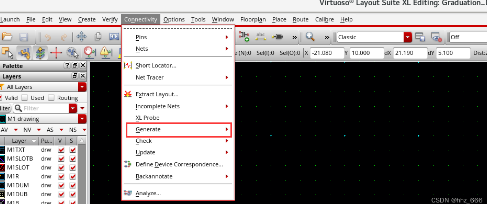

Cadence版图DRC常见错误及解决方案如下:

一、尺寸与布局错误

CT尺寸不符合

错误表现:库中CT尺寸必须为0.22μm,否则报尺寸错误及CT触及边界问题。

解决方案:检查元件封装尺寸,确保符合工艺要求。

引脚/封装边界问题

错误表现:SN和SP需包围多晶硅AA区域0.35μm上面,否则报边界错误。

解决方案:调整封装位置,确保覆盖关键区域。

二、元件引用与封装错误

元件封装重复引用

错误表现:修改多封装器件时,同一元件被分配到不同封装类型,导致DRC报错。

解决方案:在Design Cache中选中修改后的封装,右键选择“Replace Cache”更新引用。

封装缺失或属性错误

错误表现:元件封装未定义或属性(如PCB Footprint)缺失,导致DRC报错。

解决方案:检查元件封装定义,确保所有必要属性已正确配置。

三、布线与连接问题

走线间距违规

错误表现:走线与形状间距小于工艺允许值(如MIL约束),报DFA/Spatial Violation。

解决方案:调整走线间距或优化布线路径,满足工艺规则。

悬空线/未连接线路

错误表现:未连接的线路因网络标号被误认为连接,导致DRC报错。

解决方案:检查网络标号设置,删除悬空线或重新连接线路。

四、其他常见错误

重复引脚/元件名

错误表现:原理图或版图中存在重复的GND等引脚名,报Duplicate Pin Name错误。

解决方案:重新编号重复引脚,确保唯一性。

文件关联错误

错误表现:DRC文件未正确关联,报“无外部文件扩展名”错误。

解决方案:检查文件路径设置,确保DRC文件与原理图正确关联。

总结 :DRC错误多与尺寸、封装、布线规则及文件关联相关,需结合具体错误信息逐一排查。建议优先检查元件封装定义和网络标号设置,必要时使用Calibre等工具辅助验证。

一、尺寸与布局错误

CT尺寸不符合

错误表现:库中CT尺寸必须为0.22μm,否则报尺寸错误及CT触及边界问题。

解决方案:检查元件封装尺寸,确保符合工艺要求。

引脚/封装边界问题

错误表现:SN和SP需包围多晶硅AA区域0.35μm上面,否则报边界错误。

解决方案:调整封装位置,确保覆盖关键区域。

二、元件引用与封装错误

元件封装重复引用

错误表现:修改多封装器件时,同一元件被分配到不同封装类型,导致DRC报错。

解决方案:在Design Cache中选中修改后的封装,右键选择“Replace Cache”更新引用。

封装缺失或属性错误

错误表现:元件封装未定义或属性(如PCB Footprint)缺失,导致DRC报错。

解决方案:检查元件封装定义,确保所有必要属性已正确配置。

三、布线与连接问题

走线间距违规

错误表现:走线与形状间距小于工艺允许值(如MIL约束),报DFA/Spatial Violation。

解决方案:调整走线间距或优化布线路径,满足工艺规则。

悬空线/未连接线路

错误表现:未连接的线路因网络标号被误认为连接,导致DRC报错。

解决方案:检查网络标号设置,删除悬空线或重新连接线路。

四、其他常见错误

重复引脚/元件名

错误表现:原理图或版图中存在重复的GND等引脚名,报Duplicate Pin Name错误。

解决方案:重新编号重复引脚,确保唯一性。

文件关联错误

错误表现:DRC文件未正确关联,报“无外部文件扩展名”错误。

解决方案:检查文件路径设置,确保DRC文件与原理图正确关联。

总结 :DRC错误多与尺寸、封装、布线规则及文件关联相关,需结合具体错误信息逐一排查。建议优先检查元件封装定义和网络标号设置,必要时使用Calibre等工具辅助验证。