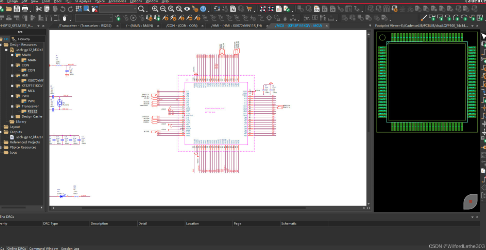

cadence画pcb流程图

软件: cadence

Cadence PCB设计流程图及关键步骤说明

一、前处理:PCB设计前的准备工作

前处理是PCB设计的基础,主要完成原理图设计与元件封装准备,确保后续PCB设计的准确性。

原理图设计:使用Cadence Capture软件绘制电路原理图,定义电路的拓扑结构、元件连接关系及基本参数(如电阻阻值、电容容量)。

创建网络表:原理图绘制完成后,通过Capture生成网络表(包含pstxnet.dat、pstxprt.dat、pstchip.dat三个文件),网络表是原理图与PCB之间的桥梁,用于传递元件封装信息和连接关系。

建立元器件封装库:检查原理图中所有元件是否有对应封装,若元件库中没有所需封装,需手动创建(包括封装外形、引脚定义、焊盘尺寸),并保存至指定目录。

创建机械设计图:设置PCB外框尺寸、高度限制、安装孔位置等信息,生成机械图文件(Mechanical Drawing),作为PCB设计的物理边界参考。

二、中处理:PCB核心设计阶段

中处理是PCB设计的关键环节,涉及元件布局、布线及信号完整性优化。

读取网络表:将Capture生成的网络表导入Cadence Allegro PCB Editor,软件自动识别元件封装和连接关系,建立原理图与PCB的关联。

摆放元件:

先摆放机械图(如板框、安装孔);

再摆放关键元器件(如I/O端口器件、集成电路、连接器),优先考虑信号流向和散热需求;

最后摆放小型元器件(如电阻、电容),遵循“先大后小、先关键后次要”的原则,优化布局以减少信号干扰。

设置层面结构:根据电路规模和EMC要求,设置PCB层叠结构(如4层板:TOP信号层、GND内电层、POWER内电层、BOTTOM信号层;6层板及上面需增加信号层或内电层),合理分配信号层与内电层的位置,抑制电磁干扰。

布线设计:

手工布线:针对关键信号(如高速信号、时钟信号),采用手工布线优化路径,确保信号完整性(如控制走线长度、阻抗匹配);

自动布线:使用Allegro的自动布线工具(如SPECCTRA)快速完成剩余信号布线,提高设计效率;

结合两者优势,兼顾布线速度与质量。

放置测试点:在电路板上放置测试点(如探针点、过孔),用于后续生产测试(如ICT测试),确保电路板功能正常。

三、后处理:PCB输出与生产准备

后处理是将PCB设计转化为生产文件的关键步骤,确保制造商能准确理解设计意图。

文字面处理:调整元器件序号、注释等文字的大小和位置,使其清晰易读;使用Back Annotation命令将PCB中的修改同步到原理图(如元件封装替换、引脚调整)。

底片处理(光绘文件生成):

设置各层组合(如TOP层、BOTTOM层、阻焊层、丝印层、钻孔层);

输出Gerber文件(RS274-X格式,行业通用),包含所有PCB层的信息(电气层、阻焊层、丝印层),供制造商制作光绘底片;

生成钻孔文件(.drl格式),包含通孔、过孔的坐标和尺寸信息,用于数控机床钻孔。

报表处理:生成生产所需的各种报表,包括:

BOM表(Bill of Material Report):列出所有元器件的型号、数量、封装;

元器件坐标报表(Component Location Report):记录每个元器件的位置(X/Y坐标);

信号线节点报表(Net List Report):验证元件间的连接关系;

测试点报表(Testpin Report):汇总测试点信息。

四、关键注意事项

层叠结构设计:多层PCB的内电层需合理分配(如GND层、POWER层),高速信号尽量走在内电层之间,减少辐射干扰;

DRC检查:布线完成后,运行Design Rule Check(DRC),检查设计是否符合电气规则(如线宽、间距、过孔尺寸),避免生产错误;

丝印处理:调整丝印层(如元件封装文字、板名)的位置和大小,避免与走线或焊盘重叠,确保清晰可见。

一、前处理:PCB设计前的准备工作

前处理是PCB设计的基础,主要完成原理图设计与元件封装准备,确保后续PCB设计的准确性。

原理图设计:使用Cadence Capture软件绘制电路原理图,定义电路的拓扑结构、元件连接关系及基本参数(如电阻阻值、电容容量)。

创建网络表:原理图绘制完成后,通过Capture生成网络表(包含pstxnet.dat、pstxprt.dat、pstchip.dat三个文件),网络表是原理图与PCB之间的桥梁,用于传递元件封装信息和连接关系。

建立元器件封装库:检查原理图中所有元件是否有对应封装,若元件库中没有所需封装,需手动创建(包括封装外形、引脚定义、焊盘尺寸),并保存至指定目录。

创建机械设计图:设置PCB外框尺寸、高度限制、安装孔位置等信息,生成机械图文件(Mechanical Drawing),作为PCB设计的物理边界参考。

二、中处理:PCB核心设计阶段

中处理是PCB设计的关键环节,涉及元件布局、布线及信号完整性优化。

读取网络表:将Capture生成的网络表导入Cadence Allegro PCB Editor,软件自动识别元件封装和连接关系,建立原理图与PCB的关联。

摆放元件:

先摆放机械图(如板框、安装孔);

再摆放关键元器件(如I/O端口器件、集成电路、连接器),优先考虑信号流向和散热需求;

最后摆放小型元器件(如电阻、电容),遵循“先大后小、先关键后次要”的原则,优化布局以减少信号干扰。

设置层面结构:根据电路规模和EMC要求,设置PCB层叠结构(如4层板:TOP信号层、GND内电层、POWER内电层、BOTTOM信号层;6层板及上面需增加信号层或内电层),合理分配信号层与内电层的位置,抑制电磁干扰。

布线设计:

手工布线:针对关键信号(如高速信号、时钟信号),采用手工布线优化路径,确保信号完整性(如控制走线长度、阻抗匹配);

自动布线:使用Allegro的自动布线工具(如SPECCTRA)快速完成剩余信号布线,提高设计效率;

结合两者优势,兼顾布线速度与质量。

放置测试点:在电路板上放置测试点(如探针点、过孔),用于后续生产测试(如ICT测试),确保电路板功能正常。

三、后处理:PCB输出与生产准备

后处理是将PCB设计转化为生产文件的关键步骤,确保制造商能准确理解设计意图。

文字面处理:调整元器件序号、注释等文字的大小和位置,使其清晰易读;使用Back Annotation命令将PCB中的修改同步到原理图(如元件封装替换、引脚调整)。

底片处理(光绘文件生成):

设置各层组合(如TOP层、BOTTOM层、阻焊层、丝印层、钻孔层);

输出Gerber文件(RS274-X格式,行业通用),包含所有PCB层的信息(电气层、阻焊层、丝印层),供制造商制作光绘底片;

生成钻孔文件(.drl格式),包含通孔、过孔的坐标和尺寸信息,用于数控机床钻孔。

报表处理:生成生产所需的各种报表,包括:

BOM表(Bill of Material Report):列出所有元器件的型号、数量、封装;

元器件坐标报表(Component Location Report):记录每个元器件的位置(X/Y坐标);

信号线节点报表(Net List Report):验证元件间的连接关系;

测试点报表(Testpin Report):汇总测试点信息。

四、关键注意事项

层叠结构设计:多层PCB的内电层需合理分配(如GND层、POWER层),高速信号尽量走在内电层之间,减少辐射干扰;

DRC检查:布线完成后,运行Design Rule Check(DRC),检查设计是否符合电气规则(如线宽、间距、过孔尺寸),避免生产错误;

丝印处理:调整丝印层(如元件封装文字、板名)的位置和大小,避免与走线或焊盘重叠,确保清晰可见。

武汉格发信息技术有限公司,格发许可优化管理系统可以帮你评估贵公司软件许可的真实需求,再低成本合规性管理软件许可,帮助贵司提高软件投资回报率,为软件采购、使用提供科学决策依据。支持的软件有: CAD,CAE,PDM,PLM,Catia,Ugnx, AutoCAD, Pro/E, Solidworks ,Hyperworks, Protel,CAXA,OpenWorks LandMark,MATLAB,Enovia,Winchill,TeamCenter,MathCAD,Ansys, Abaqus,ls-dyna, Fluent, MSC,Bentley,License,UG,ug,catia,Dassault Systèmes,AutoDesk,Altair,autocad,PTC,SolidWorks,Ansys,Siemens PLM Software,Paradigm,Mathworks,Borland,AVEVA,ESRI,hP,Solibri,Progman,Leica,Cadence,IBM,SIMULIA,Citrix,Sybase,Schlumberger,MSC Products...