cadence画原理图

软件: cadence

Cadence原理图绘制流程(以OrCAD Capture CIS为例)

1. 新建工程

启动Cadence OrCAD Capture CIS后,通过File→New→Project创建新工程。在弹出的对话框中输入工程名称(如“MyDesign”)、选择存储路径,点击“OK”。工程创建后,右侧会生成SCHEMATIC1文件夹(默认包含PAGE1原理图页),左侧Project Manager中可管理工程文件(如原理图、库、网表等)。

2. 添加/新建元器件库

2.1 加载现有库

若使用软件自带或第三方元器件库,可在PAGE1原理图页点击Place Part(放置元件),在弹出的“Place Part”窗口中,点击Libraries栏的“+”号,添加库文件(如“analog.olb”“digital.olb”),即可浏览并选择元件(如电阻、电容、芯片)。

2.2 新建自定义库

若需创建自定义元器件(如芯片、特殊器件),右键Project Manager中的Library文件夹,选择New→Library,生成library1.olb文件(可重命名,如“MyComponents.olb”)。右键该库文件,选择New Part(新建元件),在“New Part Properties”窗口中输入元件名称(如“AMS1117”)、前缀(如“U”)、封装信息(可选,后续可修改),点击“OK”进入元件绘制界面。

3. 绘制原理图

3.1 设置页面与栅格

双击SCHEMATIC1中的PAGE1,在“Schematic Page Properties”窗口中设置页面大小(如A4)、方向(Portrait/Landscape);通过Options→Preference→Grid Display调整栅格(如50mil显示栅格、100mil可见栅格),确保元件与连线对齐。

3.2 放置元件

点击Place Part,在“Place Part”窗口的Libraries栏选择库(如自定义库“MyComponents.olb”),找到目标元件(如“AMS1117”),点击“Place”将其放置在原理图中。可按Ctrl+拖动复制元件,按R键旋转元件,按X键镜像元件。

3.3 放置网络与引脚

引脚:元件放置后,会自动生成引脚(如AMS1117的VCC、GND、OUT)。若需手动添加引脚,点击Place Pin,设置引脚名称(如“IN”“OUT”)、编号(如“1”“2”)、类型(Short短线,便于紧凑布局),点击“Place”完成。

网络标签:同一页面内的电气连接可使用Place Net Alias(放置网络别名,快捷键“N”),输入网络名称(如“VCC”“GND”),点击放置。不同页面的连接需使用Off-Page Connector(页面连接器)。

3.4 连线与调整

点击Place Wire(放置连线,快捷键“W”),连接元件引脚。连线时可捕捉栅格(默认开启),确保线条整齐。若需调整连线,可点击Edit→Stretch(拉伸)或Edit→Move(移动)元件/连线,按Q键可查看元件/网络的属性(如引脚编号、网络名称)。

4. 检查与优化

4.1 电气规则检查(ERC)

点击Tools→Check→ERC(电气规则检查),选择检查规则(如“Unconnected Pins”“Duplicate Nets”),点击“Run”。检查结果会显示错误或警告,双击错误可定位到对应元件/引脚,修改后重新检查。

4.2 自动编号

点击Tools→Annotate(自动编号),在“Annotate”窗口中选择编号规则(如“Top-Down”“Sequential”),点击“OK”。软件会自动为元件分配位号(如R1、C2、U3),避免手动编号的繁琐。

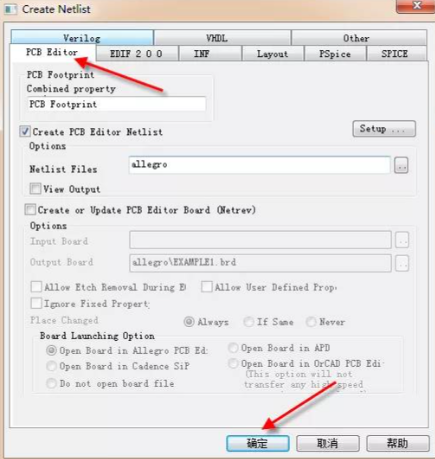

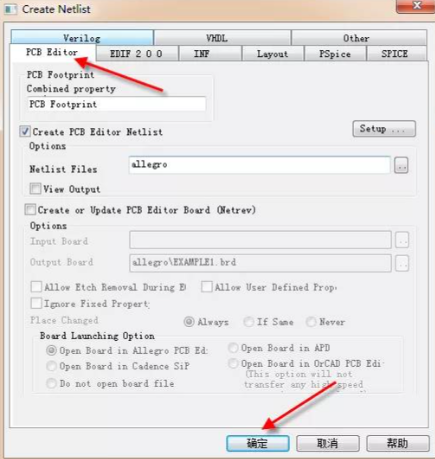

5. 生成网表

完成原理图绘制与检查后,点击Tools→Create Netlist(创建网表),选择网表格式(如“OrCAD PCB Editor”“Allegro”),点击“OK”。网表文件(如“.NET”)会保存在工程目录的Output文件夹中,用于后续PCB设计(导入元件封装与网络连接)。

注意事项

元件封装:绘制元件时,需关联PCB封装(如AMS1117的“SOT-223”封装),可在“New Part Properties”窗口的“PCB Footprint”栏输入封装名称,后续PCB设计时会自动匹配。

层次化设计:复杂电路可采用层次化设计(TOP-DOWN/BOTTOM-UP),将顶层原理图拆分为多个子模块(如“Power”“Signal_Processing”),每个子模块绘制独立的原理图,通过Block(块)命令调用,提高设计效率。

快捷键使用:熟练使用快捷键(如“P”放置元件、“W”放置连线、“Q”查看属性、“Ctrl+Z”撤销)可大幅提升绘制速度。

1. 新建工程

启动Cadence OrCAD Capture CIS后,通过File→New→Project创建新工程。在弹出的对话框中输入工程名称(如“MyDesign”)、选择存储路径,点击“OK”。工程创建后,右侧会生成SCHEMATIC1文件夹(默认包含PAGE1原理图页),左侧Project Manager中可管理工程文件(如原理图、库、网表等)。

2. 添加/新建元器件库

2.1 加载现有库

若使用软件自带或第三方元器件库,可在PAGE1原理图页点击Place Part(放置元件),在弹出的“Place Part”窗口中,点击Libraries栏的“+”号,添加库文件(如“analog.olb”“digital.olb”),即可浏览并选择元件(如电阻、电容、芯片)。

2.2 新建自定义库

若需创建自定义元器件(如芯片、特殊器件),右键Project Manager中的Library文件夹,选择New→Library,生成library1.olb文件(可重命名,如“MyComponents.olb”)。右键该库文件,选择New Part(新建元件),在“New Part Properties”窗口中输入元件名称(如“AMS1117”)、前缀(如“U”)、封装信息(可选,后续可修改),点击“OK”进入元件绘制界面。

3. 绘制原理图

3.1 设置页面与栅格

双击SCHEMATIC1中的PAGE1,在“Schematic Page Properties”窗口中设置页面大小(如A4)、方向(Portrait/Landscape);通过Options→Preference→Grid Display调整栅格(如50mil显示栅格、100mil可见栅格),确保元件与连线对齐。

3.2 放置元件

点击Place Part,在“Place Part”窗口的Libraries栏选择库(如自定义库“MyComponents.olb”),找到目标元件(如“AMS1117”),点击“Place”将其放置在原理图中。可按Ctrl+拖动复制元件,按R键旋转元件,按X键镜像元件。

3.3 放置网络与引脚

引脚:元件放置后,会自动生成引脚(如AMS1117的VCC、GND、OUT)。若需手动添加引脚,点击Place Pin,设置引脚名称(如“IN”“OUT”)、编号(如“1”“2”)、类型(Short短线,便于紧凑布局),点击“Place”完成。

网络标签:同一页面内的电气连接可使用Place Net Alias(放置网络别名,快捷键“N”),输入网络名称(如“VCC”“GND”),点击放置。不同页面的连接需使用Off-Page Connector(页面连接器)。

3.4 连线与调整

点击Place Wire(放置连线,快捷键“W”),连接元件引脚。连线时可捕捉栅格(默认开启),确保线条整齐。若需调整连线,可点击Edit→Stretch(拉伸)或Edit→Move(移动)元件/连线,按Q键可查看元件/网络的属性(如引脚编号、网络名称)。

4. 检查与优化

4.1 电气规则检查(ERC)

点击Tools→Check→ERC(电气规则检查),选择检查规则(如“Unconnected Pins”“Duplicate Nets”),点击“Run”。检查结果会显示错误或警告,双击错误可定位到对应元件/引脚,修改后重新检查。

4.2 自动编号

点击Tools→Annotate(自动编号),在“Annotate”窗口中选择编号规则(如“Top-Down”“Sequential”),点击“OK”。软件会自动为元件分配位号(如R1、C2、U3),避免手动编号的繁琐。

5. 生成网表

完成原理图绘制与检查后,点击Tools→Create Netlist(创建网表),选择网表格式(如“OrCAD PCB Editor”“Allegro”),点击“OK”。网表文件(如“.NET”)会保存在工程目录的Output文件夹中,用于后续PCB设计(导入元件封装与网络连接)。

注意事项

元件封装:绘制元件时,需关联PCB封装(如AMS1117的“SOT-223”封装),可在“New Part Properties”窗口的“PCB Footprint”栏输入封装名称,后续PCB设计时会自动匹配。

层次化设计:复杂电路可采用层次化设计(TOP-DOWN/BOTTOM-UP),将顶层原理图拆分为多个子模块(如“Power”“Signal_Processing”),每个子模块绘制独立的原理图,通过Block(块)命令调用,提高设计效率。

快捷键使用:熟练使用快捷键(如“P”放置元件、“W”放置连线、“Q”查看属性、“Ctrl+Z”撤销)可大幅提升绘制速度。

武汉格发信息技术有限公司,格发许可优化管理系统可以帮你评估贵公司软件许可的真实需求,再低成本合规性管理软件许可,帮助贵司提高软件投资回报率,为软件采购、使用提供科学决策依据。支持的软件有: CAD,CAE,PDM,PLM,Catia,Ugnx, AutoCAD, Pro/E, Solidworks ,Hyperworks, Protel,CAXA,OpenWorks LandMark,MATLAB,Enovia,Winchill,TeamCenter,MathCAD,Ansys, Abaqus,ls-dyna, Fluent, MSC,Bentley,License,UG,ug,catia,Dassault Systèmes,AutoDesk,Altair,autocad,PTC,SolidWorks,Ansys,Siemens PLM Software,Paradigm,Mathworks,Borland,AVEVA,ESRI,hP,Solibri,Progman,Leica,Cadence,IBM,SIMULIA,Citrix,Sybase,Schlumberger,MSC Products...